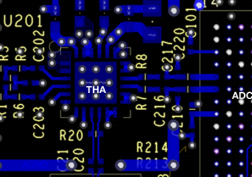

圖1. 采樣保持拓撲結構:(1a) 單列,(1b) 雙列。

延遲映射THA和ADC

開發采樣保持器和ADC信號鏈的最困難任務之一,是在THA捕獲采樣事件的時刻與應將其移到ADC上以對該事件重新采樣的時刻之 間設置適當的時序延遲。設置兩個高效采樣系統之間的理想時間差的過程被稱為延遲映射。

在電路板上完成該過程可能冗長乏味,因為紙面分析可能不會考慮PCB板上時鐘走線傳播間隔造成的相應延遲,內部器件組延遲,ADC孔徑延遲,以及將時鐘分為兩個不同段所涉及到的相關電路(一條時鐘走線用于THA,另一條時鐘走線用于ADC)。設置THA和ADC之間延遲的一種方法是使用可變延遲線。這些器件可以是有源或無源的,目的是正確對準THA采樣過程的時間并將其交給ADC進行采樣。這保證了ADC對THA輸出波形的穩定保持模式部分進行采樣,從而準確表示輸入信號。

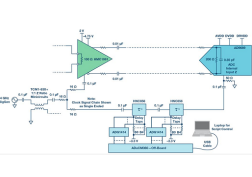

如圖2所示, HMC856 可用來啟動該延遲。它是一款5位QFN封裝,90 ps的固有延遲,步進為3 ps或25ps ,32位的高速延時器。它的缺點是要設定/遍歷每個延遲設置。要使能新的延遲設置,HMC856上的每個位/引腳都需要拉至負電壓。因此,通過焊接下拉電阻在32種組合中找到最佳延遲設置會是一項繁瑣的任務,為了解決這個問題,ADI使用串行控制的SPST開關和板外微處理器來幫助更快完成延遲設置過程。

圖2. 延遲映射電路。

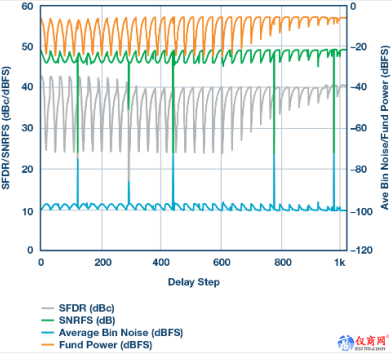

為了獲得最佳延遲設置,將一個信號施加于THA和ADC組合,該信號應在ADC帶寬范圍之外。本例中,我們選擇一個約10 GHz的信號,并施加-6 dBFS的電平(在FFT顯示屏上捕獲)。延遲設置現在以二 進制步進方式掃描,信號的電平和頻率保持恒定。在掃描過程中顯示并捕獲FFT,收集每個延遲設置對應的基波功率和無雜散動態范圍 (SFDR) 數值。

結果如圖3a所示,基波功率、SFDR和SNR將隨所應用的每個設置而變化。如圖所示,當把采樣位置放在更好的地方(THA將樣本送至ADC的過程之中)時,基波功率將處于最高水平,而SFDR應處于最佳性能(即最低)。圖3b為延遲映射掃描的放大視圖,延遲設定點為671,即延遲應該保持固定于此窗口/位置。請記住,延遲映射程序僅對系統的相關采樣頻率有效,如果設計需要不同的采樣時鐘,則需要重新掃描。本例中,采樣頻率為4 GHz,這是該信號鏈中使用的THA器件的最高采樣頻率。