ADC輸入的過驅(qū)一般發(fā)生于驅(qū)動(dòng)放大器電軌遠(yuǎn)遠(yuǎn)大于ADC最大輸入范圍時(shí),例如,放大器采用±15 V供電,而ADC輸入為0至5V。高壓電軌用于接受±10 V輸入,同時(shí)給ADC前端信號(hào)調(diào)理/驅(qū)動(dòng)級(jí)供電,這在工業(yè)設(shè)計(jì)中很常見,PLC模塊就是這種情況。如果在驅(qū)動(dòng)放大器電軌上發(fā)生故障狀況,則可因超過最大額定值 而損壞ADC,或在多ADC系統(tǒng)中干擾同步/后續(xù)轉(zhuǎn)換。本文將重點(diǎn)討論如何保護(hù)精密SAR ADC,如AD798x系列,但也適用于其他ADC類型。

試考慮圖1中的情形。

圖1. 精密ADC設(shè)計(jì)的典型電路圖。

本電路代表AD798X(例如AD7980)系列PulSAR® ADC中的情形。 輸入端、基準(zhǔn)電壓源和接地之間存在保護(hù)二極管。這些二極管 能夠處理最高130mA的大電流,但僅能持續(xù)數(shù)毫秒,不適用于 較長(zhǎng)時(shí)間或重復(fù)過壓。在一些產(chǎn)品上,例如AD768X/AD769x(如AD7685、AD7691)系列器件,保護(hù)二極管連接至VDD引腳而不是REF。在這些器件上,VDD電壓始終大于或等于REF。一般而言, 此配置更有效,因?yàn)閂DD是更穩(wěn)定的箝位電軌,對(duì)干擾不敏感。在此情況中,之所以選擇肖特基二極管,是因?yàn)槠渚哂械驼驅(qū)▔航担稍贏DC內(nèi)的內(nèi)部保護(hù)二極管之前開啟。如果內(nèi)部二極管部分開啟,肖特基二極管后的串聯(lián)電阻也有助于將電流限制在ADC內(nèi)。對(duì)于額外保護(hù),如果基準(zhǔn)電壓源沒有/幾乎沒有 灌電流能力,則可在基準(zhǔn)節(jié)點(diǎn)上采用齊納二極管或箝位電路,以圖1中,如果放大器趨向+15 V電軌,則連接至REF的保護(hù)二極管將開啟,放大器將嘗試上拉REF節(jié)點(diǎn)。如果REF節(jié)點(diǎn)未通過強(qiáng)驅(qū)動(dòng)器電路驅(qū)動(dòng),則REF節(jié)點(diǎn)(及輸入)的電壓將升至絕對(duì)最大額定電壓以上,一旦電壓在該過程中超過器件的擊穿電壓,ADC可能受損。圖3舉例說明了ADC驅(qū)動(dòng)器趨向8 V而使基準(zhǔn)電壓(5 V)過驅(qū)的情況。許多精密基準(zhǔn)電壓源無灌電流能力,這在此情形中會(huì)造成問題。或者,基準(zhǔn)驅(qū)動(dòng)電路非常強(qiáng)勁,足以將基準(zhǔn)電壓保持在標(biāo)稱值附近,但仍將偏離精確值。

在共用一個(gè)基準(zhǔn)電壓源的同步采樣多ADC系統(tǒng)中,其他ADC上的轉(zhuǎn)換不精確,因?yàn)樵撓到y(tǒng)依賴于高度精確的基準(zhǔn)電壓。如果故障狀況恢復(fù)時(shí)間較長(zhǎng),后續(xù)轉(zhuǎn)換也可能不精確。

緩解此問題有幾種不同方法。最常見的是使用肖特基二極管(BAT54系列),將放大器輸出鉗位在ADC范圍。相關(guān)說明詳見圖2和圖3。如果適合應(yīng)用需求,也可使用二極管將輸入箝位在放大器。

圖2. 精密ADC設(shè)計(jì)的典型電路圖(添加了肖特基二極管和齊納二極管保護(hù))。

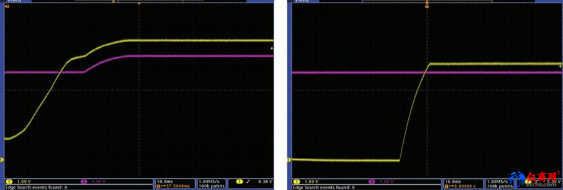

圖3. 黃色 = ADC輸入,紫色 = 基準(zhǔn)電壓源。左側(cè)圖像未添加肖特基二極管,右側(cè)圖像添加了肖特基二極管。

在此情況中,之所以選擇肖特基二極管,是因?yàn)槠渚哂械驼驅(qū)▔航担稍贏DC內(nèi)的內(nèi)部保護(hù)二極管之前開啟。如果內(nèi)部二極管部分開啟,肖特基二極管后的串聯(lián)電阻也有助于將電流限制在ADC內(nèi)。對(duì)于額外保護(hù),如果基準(zhǔn)電壓源沒有/幾乎沒有灌電流能力,則可在基準(zhǔn)節(jié)點(diǎn)上采用齊納二極管或箝位電路,以保證基準(zhǔn)電壓不被過度拉高。在圖2中,為5V基準(zhǔn)電壓源使用了5.6V齊納二極管。

圖4中的示例顯示了以正弦波使ADC輸入過驅(qū)時(shí),給ADC輸入添加肖特基二極管后對(duì)基準(zhǔn)輸入(5 V)的影響。肖特基二極管接地,5 V系統(tǒng)電軌能夠吸電流。如果沒有肖特基二極管,當(dāng)輸入超過基準(zhǔn)電壓和地電壓一個(gè)壓降時(shí),就會(huì)出現(xiàn)基準(zhǔn)電壓源干擾。從圖中可看到,肖特基二極管完全消除了基準(zhǔn)電壓源干擾。