時鐘設定發射機中的位跳變定時及接收機中的分片器定時。分布式時鐘為相關組件提供了一個常用的定時基準,可以在示波器上直觀觀察分布式時鐘。

在嵌入式時鐘系統中,我們不能直接觀測時鐘信號。振蕩器集成在發射機芯片中,接收機從數據中恢復時鐘信號。CR(時鐘恢復)電路使用PLL(鎖相環)、DLL(延遲鎖定環路)或類似技術從數據跳變中提取數據速率時鐘。嵌入式時鐘較分布式時鐘有多種優勢:第一,它們不要求額外的軌跡完成分布;第二,它們會過濾低頻抖動。

時鐘噪聲作為隨機性抖動和/或周期性抖動傳播到信號上。如果數據速率時鐘上的隨機性抖動太高,那么時鐘相噪可能會引發問題。盡管相噪在時鐘上不可避免,但如果觀察到有大量的周期性抖動,則表明出現了問題。

分析分布式時鐘上的抖動

由于分布式時鐘系統中的示波器探頭可以接入時鐘,所以我們可以在MSO6B的Spectrum View頻譜視圖中分析時鐘。諧振應該銳利、窄,沒有諧波雜散信號。所有諧振都有一些近載波相噪,也就是隨機性抖動的來源,但如果諧振寬且呈塊狀,并且白噪聲過高,那么這種諧振則是由于電子器件有噪聲、電阻器件或電子器件過熱引起的。雜散信號會引起周期性抖動,可能是由于振動和EMI引起的,其可能來自PDN。

圖4: 時鐘頻譜(頂部)和時鐘信號(底部)

圖4所示的時鐘頻譜和波形擁有干凈銳利的諧振,但有許多雜散信號,約比諧振低50dB,在時域中會看到其影響。雜散信號在數據信號中可能會導致周期性抖動,但借助手邊的雜散信號頻率,我們通常能夠找到問題,只需檢查系統設計中的振蕩器或開關電路是否會在這些頻率產生EMI輻射。

分析嵌入式時鐘上的抖動

在大多數情況下,嵌入式時鐘系統中的發射機和接收機都不能通過引腳接入基準時鐘或恢復的時鐘,但我們仍能分析它。為了把時鐘與系統的其他方面分開,我們可以分析重復的測試碼型:固定數量的0,后面跟著相同數量的1,如01010。交替碼型的優點是可以去除與位序列有關的抖動,也就是DDJ (數據相關抖動)。

從數據中恢復時鐘,使得接收機能夠追蹤低頻抖動。低于CR帶寬的抖動會同時出現在數據和時鐘上,確定分片器樣點位置。在分片器的定時擁有的抖動幅度和相位與信號相同時,該抖動不會導致錯誤。

另一方面,高于CR帶寬的頻率上的抖動可能會導致錯誤。CR帶寬由標準指定,其通常由黃金PLL設置(即fd/1667)。為分析相關抖動頻率,示波器必須捕獲足夠的時間,包含時鐘的最低頻率成分。MSO6B在軟件中仿真時鐘恢復,可以自行配置,也可以從標準指定的PLL列表中選擇。

功率完整性問題

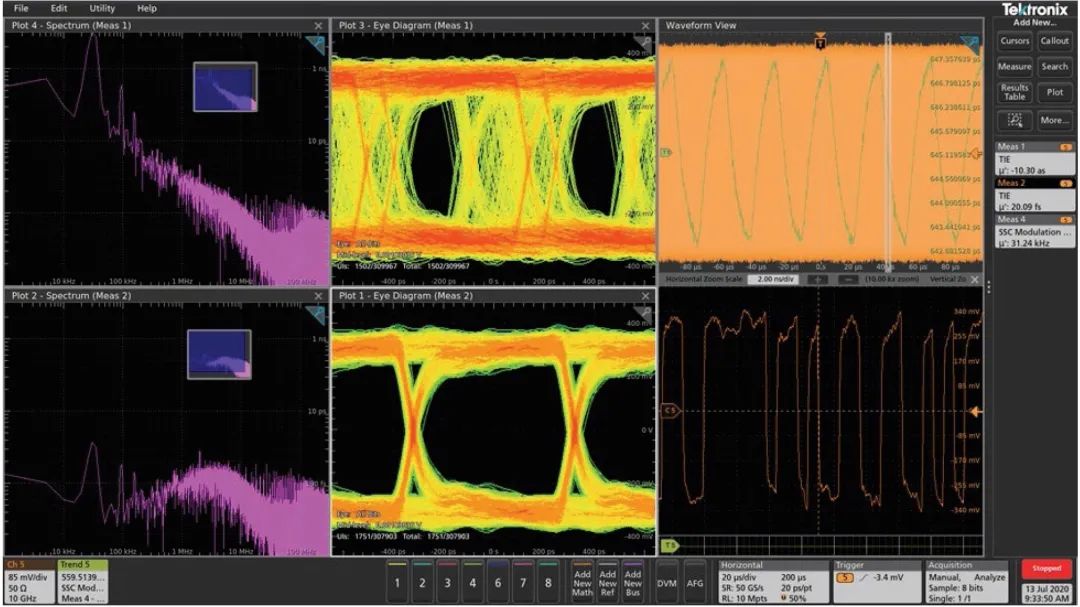

圖5顯示了低的和不同的時鐘恢復方式的影響,頂部是恒定時鐘CR,底部是二類PLL,從左到右是TIE頻譜、眼圖和波形。周期性抖動在頻譜中顯示為雜散信號,隨機性抖動顯示為噪底。

圖5. TIE頻譜、眼圖和波形,頂部是恒定時鐘CR,底部是二類PLL

在圖6頂行中,恒定時鐘頻率的抖動幅度和相位與數據抖動差異很大。結果是眼圖和波形的信號完整性差,導致高BER。在底部,二類PLL恢復的時鐘的低頻抖動與數據相同,在CR帶寬內的頻率上有效過濾了隨機性抖動和周期性抖動。結果,眼圖和波形擁有良好的信號完整性和低BER。即使是二類PLL的時鐘,TIE頻譜中的雜散信號也表明存在周期性抖動。再次對比手邊的雜散信號頻率,我們可以檢查系統設計中是否有任何器件在這些頻率上有EMI輻射,從而找到問題。

遺憾的是,解決周期性抖動問題,通常要遠比在電路中找到對應的振蕩器復雜。在沒有明顯的周期性抖動來源時,我們必須分析系統的功率完整性。電源軌道紋波經常會導致周期性抖動,有時還會導致隨機性抖動。

抖動和配電網絡