日益發展的技術對芯片電壓測試的挑戰

隨著5G、車聯網等技術的飛速發展,信號的傳輸速度越來越快,集成電路芯片的供電電壓隨之越來越小。早期芯片的供電通常是5V和3.3V,而現在高速IC的供電電壓已經到了2.5V、1.8V或1.5V,有的芯片的核電壓甚至到了1V。芯片的供電電壓越小,電壓波動的容忍度也變得越苛刻。對于這類供電電壓較小的高速芯片的電壓測試用電源噪聲表示,測求要求從±5%到 ±-1.5%,乃至更低。

如果芯片的電源噪聲沒有達到規范要求,就會影響產品的性能,乃至整機可靠性。因此工程師需要準確地測量現代電路產品中的芯片電壓的電源噪聲。

芯片電源噪聲的特點

更小幅度,更高頻率

以往電源噪聲的要求維持在幾十mV的量級,而隨著芯片電壓的降低,很多芯片的電源噪聲已經到了mV的量級,某些電源敏感的芯片要求甚至到了百uV的量級。直流電源上的噪聲是數字系統中時鐘和數據抖動的主要來源。處理器、內存等芯片對直流電源的動態負載隨著各自時鐘頻率而發生,并可能在直流電源上耦合高速瞬態變化和噪聲,它們包含了1 GHz以上的頻率成分。

因此與傳統的電源相比,芯片電源的噪聲具有頻率高/幅度小等特點,這就為了工程師準確地測得芯片的電源噪聲帶來了挑戰。

表1:傳統電源和芯片電源頻率和噪聲范圍

電源分布網絡(PDN)引入的噪聲干擾

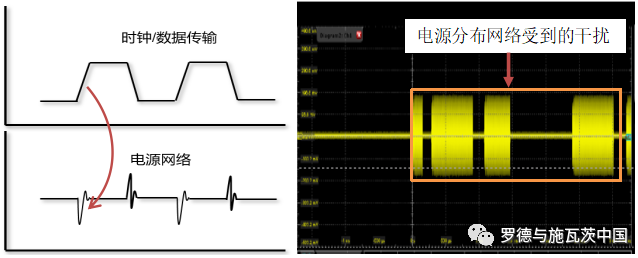

為了保證電路上各個芯片的供電,電源分布網絡(PDN)遍布整個PCB。如果電源分布網絡靠近時鐘或者數據的PCB走線,那么時鐘/數據的變化會耦合到電源分布網絡上,也會成為電源噪聲的來源。在這種情況下,工程師還需要定位電源噪聲的來源,以便后續調整PCB的布局和布線,減少PDN網絡受到的干擾。

圖2:時鐘,數據傳輸線耦合到電源分布網絡的干擾

影響電源噪聲測試準確性的因素

示波器是電源噪聲測試的重要儀器。為了能夠準確地測量GHz帶寬內mV級別的電源噪聲,并定位干擾電源分布網絡的噪聲來源,需要考慮如下因素:示波器的底噪,探頭的衰減比,示波器的偏置補償能力,探頭的探接方式,以及示波器的FFT能力等等。

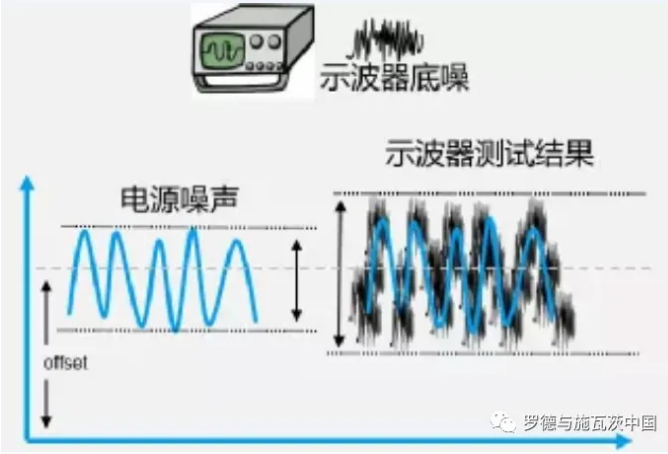

示波器底噪

圖3:示波器底噪對電源噪聲測試結果的影響

探頭的衰減比

目前最常用的500MHz帶寬的無源探頭的衰減比為10:1,其會放大示波器的底噪,影響電源噪聲測試的不確定性。

如果用傳統的衰減比為1:1的無源探頭,可以避免放大示波器的底噪。但是這種探頭的帶寬一般在38MHz,無法測到更高頻率的電源噪聲。同樣會影響電源噪聲測試的不確定性。

所以,為了準確測量電源噪聲,需要一款衰減比為1:1,帶寬到GHz的探頭。

圖4:頭的衰減比對電源噪聲測試的影響

示波器的偏置補償能力