引言

看過《三體》的朋友們,一定對震撼的人列計(jì)算機(jī)有所印象:馮 · 諾依曼讓秦始皇安排三千萬個士兵組成的人列計(jì)算器,通過士兵舉黑白旗顯現(xiàn)的信號代替了二進(jìn)制進(jìn)行運(yùn)算;通過騎馬的輕轉(zhuǎn)兵在整個系統(tǒng)間傳遞信息代替了總線進(jìn)行數(shù)據(jù)傳輸;并利用三百萬名文化程度較高的學(xué)者每個人手中的記錄本和筆,負(fù)責(zé)記錄運(yùn)算結(jié)果代替了存儲器。這就形成了控制器和運(yùn)算單元、總線以及存儲器的概念。

不知道讀者在閱讀這一段的時候是否有一個疑問,為什么不能有一個聰明的士兵既能做運(yùn)算又能記錄運(yùn)算結(jié)果,實(shí)現(xiàn)“存算一體化”, 從而降低包括數(shù)據(jù)搬移在內(nèi)所帶來的巨大開銷?

應(yīng)用背景

正像三體中描述的人列計(jì)算機(jī),目前大多數(shù)芯片系統(tǒng)采用的是馮·諾依曼架構(gòu),處理器和存儲器由總線連接,數(shù)據(jù)需在二者之間來回搬運(yùn)。但隨著大數(shù)據(jù)和人工智能時代的到來,傳統(tǒng)的計(jì)算存儲分離的硬件架構(gòu)不得不面對馮·諾伊曼瓶頸。數(shù)據(jù)搬移帶來的能耗開銷使得存算分離的傳統(tǒng)架構(gòu)難以滿足低功耗的系統(tǒng)設(shè)計(jì)需求。在一些神經(jīng)網(wǎng)絡(luò)硬件加速器中,核心的數(shù)據(jù)處理消耗的能量只有不到10%,除此之外與數(shù)據(jù)傳輸相關(guān)的能耗才是制約整個系統(tǒng)能效的關(guān)鍵問題。

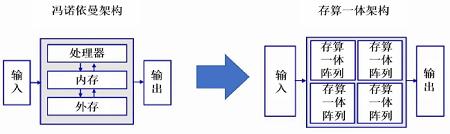

如圖1所示,為了打破馮·諾依曼瓶頸的束縛,存算一體的計(jì)算架構(gòu)開始興起,逐漸從近存儲的計(jì)算范式到以存儲為中心的計(jì)算范式演進(jìn)。近年來,半導(dǎo)體制造工藝的發(fā)展和人工智能領(lǐng)域的崛起,為存算一體技術(shù)提供了全新的制造平臺和產(chǎn)業(yè)驅(qū)動力。除了在人工智能及深度學(xué)習(xí)領(lǐng)域的廣泛應(yīng)用,存算一體架構(gòu)同樣適用于未來主流的感存算一體芯片和類腦芯片。

圖1 馮·諾依曼架構(gòu)和存算一體架構(gòu)示意圖

存算一體芯片旨在把傳統(tǒng)以計(jì)算為中心的架構(gòu)轉(zhuǎn)變?yōu)橐詳?shù)據(jù)為中心的架構(gòu),直接利用存儲器進(jìn)行數(shù)據(jù)處理。近年來非易失性存儲器技術(shù)的發(fā)展,為存算一體芯片的高效實(shí)施帶來了新的曙光。

我國在這方面的研究也取得了一系列的創(chuàng)新成果,例如2016年北京大學(xué)康晉峰教授團(tuán)隊(duì)提出以阻變器件替代傳統(tǒng)的CMOS器件來實(shí)現(xiàn)邏輯計(jì)算。構(gòu)建了基于觸發(fā)電平時序的邏輯計(jì)算類型,得到可以實(shí)時邏輯重構(gòu)的計(jì)算、存儲一體化并行處理硬件架構(gòu)。2021年,中國科學(xué)院微電子研究所的劉明團(tuán)隊(duì)設(shè)計(jì)了超薄鐵電隧道結(jié)進(jìn)行時間數(shù)據(jù)學(xué)習(xí)的節(jié)能而穩(wěn)健的儲層計(jì)算系統(tǒng),該系統(tǒng)以高的能效、處理速度 和識別精度完成數(shù)字序列分類。2021年復(fù)旦大學(xué)周鵬團(tuán)隊(duì)研究出二維鐵電溝道晶體管(2D FeCTs),該FeCTs兼具優(yōu)異的非易失存儲功能和神經(jīng)擬態(tài)能力。如圖2所示,該器件成功實(shí)現(xiàn)了對鳶尾花圖像的高精度分類。2022年國防科技大學(xué)電子科學(xué)學(xué)院徐暉教授課題組與復(fù)旦大學(xué)芯片與系統(tǒng)前沿技術(shù)研究院劉琦教授課題組合作,首次實(shí)現(xiàn)了一種與CMOS工藝完全兼容的氧化鉿基反鐵電神經(jīng)元。該反鐵電晶體管能模擬生物神經(jīng)元積分發(fā)射特性,且由于其自發(fā)的去極化現(xiàn)象避免了大尺寸電容和復(fù)位電路的使用,有效提高了神經(jīng)形態(tài)計(jì)算芯片集成度。如圖3所示構(gòu)建的784×400×10雙層神經(jīng)網(wǎng)絡(luò),手寫體識別率高達(dá)96.8%,對促進(jìn)新原理器件在圖像、語音等智能化處理場景的應(yīng)用具有重要意義。2022年,華東師范大學(xué)段純剛教授團(tuán)隊(duì)利用鐵電突觸晶體管神經(jīng)網(wǎng)絡(luò)成功實(shí)現(xiàn)了聯(lián)想學(xué)習(xí),達(dá)到輸入了不完整的像素,也可以從硬件成功輸出完整像素的圖像識別功能。

圖3 雙層全鐵電SNN示意圖及基于FeFET突觸和AFeFET神經(jīng)元網(wǎng)絡(luò)的硬件

測試方案介紹

存算一體芯片旨在把傳統(tǒng)以計(jì)算為中心的架構(gòu)轉(zhuǎn)變?yōu)橐詳?shù)據(jù)為中心的架構(gòu),直接利用存儲器進(jìn)行數(shù)據(jù)處理。存算一體芯片在當(dāng)代研究的最新神經(jīng)元網(wǎng)絡(luò)中扮演高速存儲計(jì)算單元,其主要技術(shù)路線有通過阻變,容變等方式實(shí)現(xiàn)。存算一體芯片在當(dāng)代研究的最新神經(jīng)元網(wǎng)絡(luò)中扮演高速存儲計(jì)算單元。在研發(fā)階段,目前很多機(jī)理的存算一體芯片都需要反復(fù)測試驗(yàn)證迭代,必須需要有一套合適的測試系統(tǒng)加速這一過程。在這個過程中,如何快速將單個單元的測量擴(kuò)展到陣列形式的測量,是實(shí)驗(yàn)室必須要解決的一個測量難題。

測試需求

? 單個單元的性能測試

? 可擴(kuò)展的多單元性能測試

? 存算一體陣列芯片的測試

? 模擬應(yīng)用的測試方法

陣列測試流程

1. 對陣列中的行列每個單元通過施加脈沖,進(jìn)行預(yù)設(shè)置,記錄I-V特性。

2. 預(yù)設(shè)置整體陣列后,再次對每個行列單元按序列施加脈沖,記錄充放電情況及極化反轉(zhuǎn)等特性。

3. 不同的序列脈沖施加,測試不同行列激勵下的不同反應(yīng)。

4. 測試過程中需要反復(fù)施加脈沖,并且同步測量I-V特性并需要友好方便的編程方式滿足不同的激勵測試需求