圖2. 時鐘樹框圖

這些延遲可能受外界因素的影響,比如電壓和溫度變化,以及特定器件工藝變化。這種不精確性會疊加,可能導(dǎo)致ADC和DAC無法忍受的時序偏差,而高頻時需要對其時鐘信號進行同步。現(xiàn)代系統(tǒng)所要求的高工作頻率意味著苛刻的建立和保持時間。雖然固定延遲可以通過其它方面加以補償,但不確定性延遲卻無法在系統(tǒng)中補償。因此,設(shè)計人員的目標便是通過某種方式控制不確定性延遲,最小化甚至完全消除其影響。

除這些限制外,樹形結(jié)構(gòu)應(yīng)當是靈活的,以便根據(jù)系統(tǒng)需要增加分支數(shù)量,并輕松控制它們。

實現(xiàn)時鐘對齊和通道偏斜最小化目標的常見做法是使用確定性——也就是說,重復(fù)用于所有器件和所有上電時序。在JESD204B系統(tǒng)中,需要對齊本地多幀時鐘(LMFC),以實現(xiàn)確定性延遲。接口通過子類1 (SYSREF)或子類2 (SYNC)定義調(diào)用發(fā)送和接收器件的LMFC復(fù)位與對齊。系統(tǒng)中的不確定性延遲使得在1個LFMC周期內(nèi)實現(xiàn)LMFC的對齊變得更為困難。因此,前文提到的帶高精度對齊功能的時鐘樹結(jié)構(gòu)可以幫助系統(tǒng)設(shè)計人員滿足LMFC對齊要求。

此外,設(shè)計人員還需確保在每一個數(shù)據(jù)轉(zhuǎn)換器輸入端觀察到相對于器件時鐘而言可以接受的SYSREF信號建立和保持時間。如果設(shè)計中使用了單時鐘芯片,則滿足建立和保持時間要求直接保證了具有適當?shù)臅r序裕量,而在基于簡單時鐘緩沖器的多器件時鐘樹結(jié)構(gòu)中,控制建立和保持時間的難度更大。建議的時鐘樹結(jié)構(gòu)具有不同層級之間的確定性同步,有助于滿足所有層級的全部SYSREF/器件時鐘對建立/保持時序的要求。這種時鐘樹結(jié)構(gòu)可以滿足同步限制,并在不同層級之間實現(xiàn)每一個數(shù)據(jù)轉(zhuǎn)換器高速器件時鐘的相位對齊。

時鐘樹設(shè)計

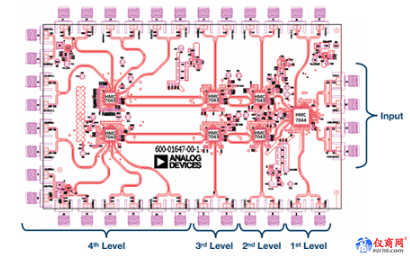

圖3顯示了一個四級時鐘樹示例,它采用了一個主時鐘生成器件(HMC7044)和三級扇出緩沖器(HMC7043)來創(chuàng)建多個同步時鐘,用于采樣板。

圖3. 四級時鐘樹示例

使用一個HMC7044器件作為時鐘樹的根;它是一個14路輸出時鐘生成器,抖動衰減支持JESD204B同步。HMC7043器件——14路輸出扇出緩沖器——用于每一級分支。這些器件完全兼容,它們的編程特性非常相似,因而可以很方便地進行器件匹配以及增加或減少時鐘分配級,提升了系統(tǒng)的靈活性。

在時鐘樹的每一級,各輸出之間也許可以實現(xiàn)同步。在本系統(tǒng)中,HMC7044的輸出可以通過SPI命令(或者使用更精確的SYNC脈沖)進行相位對齊。該命令將復(fù)位HMC7044的通用SYSREF定時器,它控制所有時鐘的輸出分頻器。所有輸出時鐘分頻器均通過SYSREF定時器命令同步對齊。SYNC命令到SYSREF定時器的延遲,以及開啟和關(guān)斷時間之間的延遲非常明確,并提供輸出之間具有確定性延遲的同步。此外,可以編程任意輸出,生成確定數(shù)量的脈沖,用作系統(tǒng)中的SYSREF脈沖。

時鐘分配器件HMC7043還含有非常相似的SYSREF定時器結(jié)構(gòu)。該器件利用RFSYNC信號來實現(xiàn)對齊。RFSYNC脈沖將啟動與HMC7044的SYNC信號相同的過程,并且所有輸出都將以高精度同步。同樣,輸出可以設(shè)為脈沖模式,用作SYSREF脈沖。

建議的時鐘樹結(jié)構(gòu)基本使用SYSREF信號作為HMC7043的下一級RFSYNC信號,同時在每一級的輸出端保持相位對齊。通過仔細的架構(gòu)設(shè)計,所有這些時序信號都可以是確定性的,從而具有嚴格的偏斜控制。此外,每個器件都包含一個模擬延遲結(jié)構(gòu),因此輸出之間的任何偏斜差異或任何線路長度的不相等都可以在源頭進行補償。

對于RF系統(tǒng)中的復(fù)雜數(shù)據(jù)轉(zhuǎn)換器陣列而言,可能需要使用不同的頻率,因為ADC、DAC、FPGA、本振和混頻器可能采用不同頻率的時鐘信號。HMC7044和HMC7043都集成了分頻器,可生成多種頻率的信號。另外,HMC7044具有雙PLL結(jié)構(gòu),集成VCO,無需額外元件即可生成高頻時鐘。

常見通信系統(tǒng)的額外復(fù)雜性在于,大部分RF前端元件依賴串行接口連接到發(fā)送/接收模塊,要求數(shù)據(jù)和時鐘通過數(shù)字處理器或FPGA來嵌入/消除。這個過程通常會產(chǎn)生干擾基準時鐘抖動,要求在較大的RF時鐘生成和分配器件中集成抖動衰減能力,比如HMC7044。

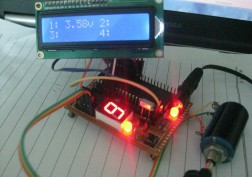

用于數(shù)據(jù)轉(zhuǎn)換器陣列的緊湊型解決方案如圖4所示。